### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

Revista Informática y Sistemas. Vol., No. XX, meses, año, páginas

ISSN 2550-6730

### Estudio de los Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

Alejandro Arteaga<sup>1</sup>, Miguel Angel Bring<sup>2</sup>, Jorge Torres Gómez<sup>3</sup>

<sup>1,2</sup>CIDP-Grito de Baire, CUBA, Santa Ana # 711 e/ 47 y Reforma, Nuevo Vedado, Plaza, La Habana <sup>2</sup>CUJAE-Facultad de Telecomunicaciones y Electrónica, La Habana, Cuba <sup>1</sup>alejandroa@gb.reduim.cu, <sup>2</sup>bring@gb.reduim.cu <sup>3</sup>jorge.tg@tele.cujae.edu.cu

#### RESUMEN

Los sistemas de espectro esparcido por salto de frecuencia (FHSS) son implementados en la actualidad para brindar mayor robustez y seguridad en las comunicaciones. Con base en el incremento de ancho de banda que experimentan las señales FHSS estas se emplean para coexistir con otras comunicaciones con un mínimo de interferencia. Las aplicaciones de su implementación se reportan de carácter comercial y militar en comunicaciones GSM, Bluetooth, entre aeronaves o para radios tácticos. En la actualidad dado el creciente incremento de tecnologías digitales como los FPGAs y los circuitos integrados se reportan diversas soluciones con el empleo de estos dispositivos. El presente trabajo aborda la descripción de estos esquemas en FPGA. Se describe por diagramas en bloque los principales esquemas así como las principales tecnologías empleadas.

PALABRAS CLAVES: FHSS, FPGA, SoC, Radio-comunicaciones.

#### ABSTRACT

Spread Spectrum systems by frequency hopping (FHSS) are currently implemented to improve robustness and security of communications. Based on the increase of bandwidth, FHSS waveforms are used to coexist with other communications signals simultaneously by producing the less interference. Commercial and military applications are exhibited on GSM, Bluetooth, Aeronautical and tactical radios. On the other hand, provided the increasing use of digital technologies like FPGA and circuits on chip, a variety of solutions are reported to use these devices. The present work is oriented to describe FHSS schemes on FPGA. Through block diagrams main description and common used technologies are presented as well.

KEYWORDS: FHSS, FPGA, SoC, Radio-communications.

### 1. INTRODUCCIÓN

Las comunicaciones por salto de frecuencia muestran aplicaciones para el ámbito militar y civil en la medida que reducen el efecto de las acciones interferentes y reducen la probabilidad de detección e intercepción de la señal. Para las aplicaciones militares resulta importante contar con sistemas de comunicación que sean difíciles de atacar por usuarios intencionados (jamming) o de dificultad para la escucha por usuarios no autorizados. En las aplicaciones civiles, dada la creciente demanda de dispositivos simultáneamente conectados, los sistemas de espectro esparcido posibilitan la interconexión de los mismos manteniendo la calidad de servicio.

Entre las aplicaciones civiles se reportan esquemas de comunicación para GSM [1], Bluetooth [2], IoT [3], Aeronaves [4] y Radar [5]. Típicamente estas transmisiones con el empleo de espectro esparcido puede compartir bandas con otras comunicaciones mediante el acceso múltiple por división de código (CDMA, por sus siglas en inglés) [6]. Entre las aplicaciones militares se encuentran los radios tácticos con las capacidades de encriptación y estrategias anti-jamming [7].

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

A. Arteaga, M. Bring, J. Torres

Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

Las comunicaciones por espectro esparcido tienen su origen en las aplicaciones militares hacia finales de la segunda guerra mundial [8]. El interés de desarrollar comunicaciones sin posibilidades de intercepción motivó la conformación y estudio de este tipo de señales. En este respecto, la descripción de diseños óptimos para servo-mecanismos fue primeramente desarrollada de forma teórica por Wiener con el empleo de correladores [9]. En adición también se evidenció la necesidad de conformar señales de carácter pseudo-aleatorio. Los estudios teóricos de Shannon indicaron que este tipo de señales son las que maximizan la capacidad de transmitir información y por tanto el mejor uso del canal de comunicaciones [10].

Desde el punto de vista práctico los primeros diseños se concibieron por radios analógicos en diversos tipos empleando saltos en el tiempo y en la frecuencia. Luego se desarrolló el empleo de codificaciones por secuencias pseudo-aleatorias mezclado con la información transmitida. Como radio para las comunicaciones de larga distancia se conformaron los primeros sistemas dados por Rake, F9C-A, ARC-50 y BLADES [8] con las características de espectro esparcido.

Los esquemas de espectro esparcido se caracterizan por el empleo de un código pseudo-aleatorio. Mediante este código se conforma la señal transmitida con propiedades muy parecidas a la de una señal de ruido, a partir de la cual se hace muy difícil recuperar la información por usuarios que no cuenten con este código. El código pseudo-aleatorio se comparte entre el transmisor y el receptor, solo mediante la sincronía del receptor con el código conformado en el transmisor es posible la recuperación del mensaje transmitido.

En la actualidad, la implementación de transmisores y receptores mediante electrónica digital posibilita la flexibilidad del diseño y la incorporación de esquemas de codificación robustos. Estas soluciones también son implementadas en FPGA por sus ventajas de cómputo paralelo hacia la obtención del sincronismo con rapidez. Entre las soluciones reportadas en FPGA para los esquemas de salto de frecuencia se encuentran las siguientes:

- Algoritmo iterativo de intercambio de mensajes (iMPAs, iterative Message Passing Algorithms)[11].

- Implementación como Radio Definido por Software (SDR) mediante la complementación de PC-FPGA [12] y mediante la complementación de circuitos integrados y FPGA [13].

- Superposición de tonos [14].

- Implementación de modulador FHSS-FSK [15].

El presente artículo describe los sistemas de espectro esparcido reportados por su implementación en FPGA. Se resumen sus principales funcionalidades y se hace un análisis comparativo de estos esquemas. La Sección 2 aborda los principios generales de las señales de espectro esparcido así como los esquemas de sincronismo. La Sección 3 muestra los diseños reportados en FPGA así como las principales tecnologías y funcionalidades. Por último la Sección 4 muestra las conclusiones.

### 2. Principios de los esquemas de espectro esparcido por salto de frecuencia

Las señales de espectro esparcido por de salto de frecuencia (FHSS, por sus siglas en inglés) son conformadas con características pseudo-aleatorias. En este sentido, la señal transmitida tiene un aspecto totalmente aleatorio, no obstante es reproducible teniendo en cuenta el código que la genera.

Los sistemas es espectro esparcido (SS, por sus siglas en inglés) se conforman por las siguientes características [16]:

- La señal esparcida ocupa un ancho de banda muy superior al mínimo ancho de banda requerido para transmitir la información.

- El esparcimiento se obtiene por la aplicación de una señal, comúnmente llamada señal de código, la cual es independiente del dato transmitido.

- En el receptor se recupera la señal de información por la correlación de la señal recibida con una réplica sincronizada de la señal de código.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

Revista Informática y Sistemas. Vol., No. XX, meses, año, páginas

ISSN 2550-6730

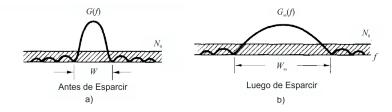

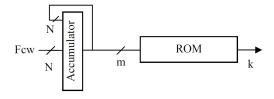

El proceso de esparcimiento se describe frecuencialmente por un aumento del ancho de banda de la señal transmitida comparativamente mucho mayor que el propio de la señal de información. Este esparcimiento se visualiza frecuencialmente como lo muestra la Figura 1. En la Figura 1 a) se muestra la señal de información por su densidad espectral G(f) antes de esparcir. En la Figura 1 b) se muestra la señal esparcida a ser transmitida. Se puede observar como la señal transmitida ocupa un ancho de banda superior al de la señal original. Este aumento del ancho de banda implica el aumento de la dimensionalidad de la señal dado por el producto tiempo-ancho de banda.

Figura 1: Efecto del esparcimiento de la señal [16]. a) Señal antes de esparcir. b) Señal luego de ser esparcida.

En la actualidad se reportan dos grupos de técnicas principales para aumentar la dimensionalidad de las señales. Estas están dadas por los siguientes esquemas [16], [17]:

- Secuencia Directa (DS, Direct Sequence Spread Spectrum): Aplicado con una modulación de doble banda lateral (DSB) ó BPSK.

- Saltos de Frecuencia (FH, Frequency Hopping): Aplicado con una modulación MFSK y en algunos casos con BPSK.

Estos dos esquemas se aplican cuando la información a transmitir es de carácter digital. Otros sistemas esparcen el espectro con la modulación FM cuando la información a transmitir es analógica.

En el receptor se verifica un proceso inverso para la recuperación de la señal original. Este proceso cancela el efecto de esparcimiento en forma inversa al mostrado en la Figura 1. En la recepción de la señal esparcida se establece la integración de la señal a su versión original pero a la vez se esparcen posibles tonos interferentes en el canal de comunicaciones. La Figura 2 a) muestra el caso de la señal recibida más la interferente, dados por  $G_X(f)$  y  $G_z(f)$ , respectivamente. Luego de aplicar el proceso inverso de esparcimiento, se obtiene un realce de la señal de información y un esparcimiento de la señal interferente en la Figura 2 b). En este sentido los sistemas de esparcimiento logran disminuir en el proceso de recepción el efecto de tonos interferentes, ya sea de forma intencionada o producto de la coexistencia con otras comunicaciones.

Figura 2: Efecto de la cancelación del esparcimiento de la señal de información  $G_X(f)$  y el esparcimiento señal interferente  $G_z(f)$  en la recepción [17]. a) Espectro de la señal recibida con superposición de tono interferente. b) Espectro de la señal luego de cancelar el efecto de esparcimiento.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

A. Arteaga, M. Bring, J. Torres

Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

El presente artículo describe el principio de funcionamiento y los esquemas de implementación en FPGA para los sistemas de salto de frecuencia (FH). Mediante un sistema por salto de frecuencia se obtiene una mayor ganancia de procesamiento dado por  $G_p = \frac{W_{ss}}{W}$  que empleando un sistema de secuencia directa, donde  $W_{ss}$  denota el ancho de banda de la señal esparcida y W el ancho de banda de la señal sin esparcir. Con el empleo de un sintetizador de frecuencia es posible lograr saltos de frecuencia en un rango mucho más amplio que su contraparte de código por secuencia directa (DS).

A diferencia del sistema DS, el sistema FH permite hacer saltos lentos y saltos rápidos [18]. Los saltos rápidos se suceden cuando la duración de un salto o el tiempo de chip es menor que el tiempo de símbolo. El salto lento es cuando ocurre lo contrario. Los saltos lentos son convenientes desde el punto de vista de hardware dado que exige menos recursos del sintetizador digital y consume menor energía. Por su parte, el salto rápido resulta menos interferido por un potencial atacante o por fading. Dado que se contamina parte de un símbolo transmitido y no varios símbolos, la información recuperada resultará más fiable. Además, el sincronismo de código se logrará en menor tiempo. Para esta técnica la modulación usualmente empleada es la MFSK, aunque algunos sistemas emplean la BPSK [17].

#### 3. Sistema de salto de frecuencia en FPGA

Entre las técnicas desarrolladas para la obtención de sincronismo en FPGA se reportan en su mayoría soluciones paralelo. Estas soluciones aunque requieren de mayor complejidad de implementación resultan las de mayor rapidez para la obtención del sincronismo con la secuencia de salto. A continuación se describe la implementación de estas soluciones en FPGA.

#### 3.1. Esquema iMPAs

El esquema de solución iMPAs resulta de la generalización de los algoritmos turbo-decoding [11] como técnica correctora de errores. De forma iterativa se va decodificando la señal recibida con el objetivo de disminuir los errores en la información recibida. De igual forma el algoritmo iMPAs va desarrollando la secuencia de salto apropiada para la reducción de errores.

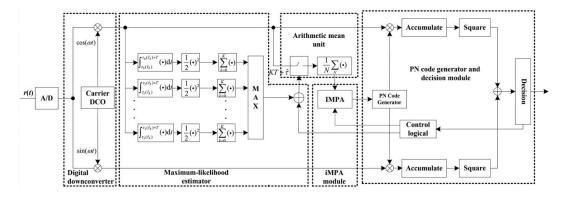

El esquema de la figura 3 muestra el receptor para la adquisición de sincronismo de señales de salto de frecuencia. El proceso de detección del arribo de la señal se realiza por una búsqueda paralelo con el estimador del maximum likelihood. Esta señal luego se acumula por dos sumadores que alimentan al bloque iMPA. En función del resultado de estos dos procesos de acumulación se modifica la secuencia de salto hasta la obtención del sincronismo. El bloque IMPA orienta la ejecución del código pseudo-aleatorio a modo de sincronizarse con el código generado en el transmisor. El algoritmo iMPAs funciona por 5 pasos según la decodificación turbo [19]. En estos pasos se actualizan valores de nodos internos y métricas para el establecimiento de la secuencia apropiada.

La implementación en FPGA se logra por varios módulos integrados en dos bloques principales, uno como controlador maestro y otro para la realización de cálculos aritméticos. La figura 4 muestra el diagrama en bloques para su implementación en FPGA. La implementación del algoritmo iMPAs así como todos los elementos del bloque de control se logra por una máquina de estados. Esta solución se reporta con buenos resultados en el intervalo de relación señal a ruido de [-15 - 10] dB.

### 3.2. Implementación como Radio Definido por Software (SDR)

En la implementación como Radio Definido por Software (SDR) se reportan dos soluciones hacia la integración con FPGAs [12]. Una de las soluciones se integra por una PC, otra de las soluciones se integra con Sistemas en Chip (SoC, System on Chip por sus siglas en inglés) como DSPs [13].

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

Revista Informática y Sistemas. Vol. , No. XX, meses, año, páginas

ISSN 2550-6730

Figura 3: Esquema de sincronismo iMPAs [11].

Figura 4: Esquema de algoritmo iMPAs para implementar en FPGA [11].

#### 3.2.1. Integración PC-FPGA

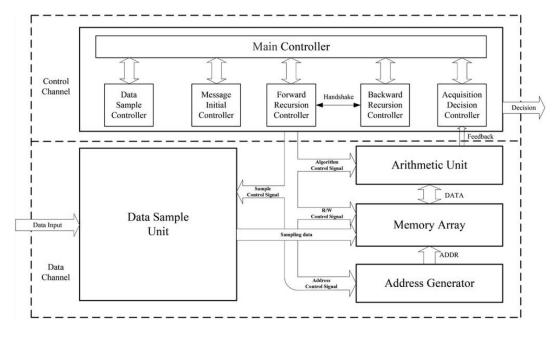

Los autores en [12] implementan una solución para las comunicaciones por salto de frecuencia mediante el empleo de una PC convencional y un FPGA. Entre ambos dispositivos se implementa un radio definido por software en la medida que la PC implementa las operaciones de procesamiento de la señal recibida y el FPGA.

Las operaciones en la PC se reportan sobre el sistema operativo XP con el procesador Pentium IV (3,2 GHz). En la PC se realiza el procesamiento de señales del estándar GSM mediante la programación por hilos. En el procesamiento de las señal se realiza el sincronismo de la señal de salto. Las operaciones del FPGA implementan un proceso de translación de frecuencia con un DDC (digital down converter).

La figura 5 muestra la integración de los distintos elementos del sistema. Bloques de amplificación y filtrado acondicionan la señal recibida para ser muestreada por el conversor A/D. Luego el FPGA realiza la traslación de frecuencia y entrega una secuencia de señal banda base en fase y en cuadratura hacia la PC. La integración entre el FPGA y la PC se realiza mediante la comunicación USB 2.0.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

A. Arteaga, M. Bring, J. Torres

Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

Figura 5: Esquema de integración PC-FPGA [12].

En este esquema la función del FPGA es la de funcionar como down-converter y cancelar el efecto de esparcimiento. El proceso de sincronismo se implementa en la PC. Es la PC la que establece los códigos apropiados para sincronizarse con el transmisor.

#### 3.2.2. Integración SoC-FPGA

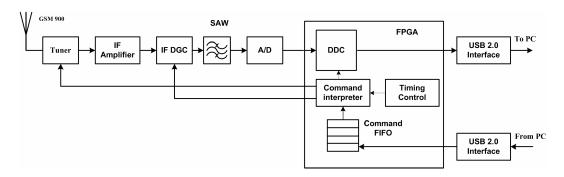

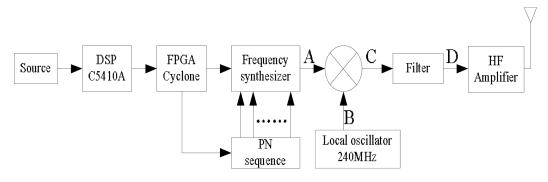

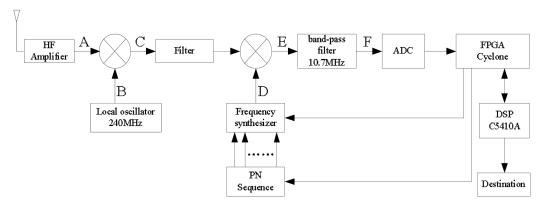

Otro de los esquemas reportados como SDR surge por la integración de SoC como circuitos integrados con el FPGA [13]. La función de estos circuitos integrados es la de complementar la generación de la señal de salto mediante sintetizadores y la de conformar la codificación de la información mediante DSPs.

La estructura hardware para el proceso de transmisión y recepción se muestra en la figura 7. Los circuitos integrados empleados en la transmisión son el DSP para la codificación de la señal y el Sintetizador de Frecuencia para conformar la señal a transmitir. Se emplean además otros bloques para conformar la señal a transmitir como multiplicador de frecuencia, filtrado y amplificación de la señal a transmitir. La función del FPGA es la de conformar la secuencia de salto para el sintetizador de frecuencia.

Para la recepción, en la figura 7 b) se muestra el esquema por bloques de acondicionamiento de la señal similares a los empleados en el transmisor. El multiplicador se emplea para colocar la señal en una frecuencia intermedia, en función inversa a los del transmisor.

Para el transmisor y el receptor el FPGA se emplea como modulador y demodulador, respectivamente. Para estos procesos se implementa digitalmente en el FPGA un oscilador controlado numéricamente (NCO, por sus siglas en inglés). La modulación empleada es la BFSK, la cual se conforma por dos frecuencias representando directamente el código binario de información.

En adición, el FPGA se implementa como recuperador de sincronía mediante la adquisición de un código cabecera. En cada trama de información se conforma una cabecera de sincronía empleando el código de Bark.

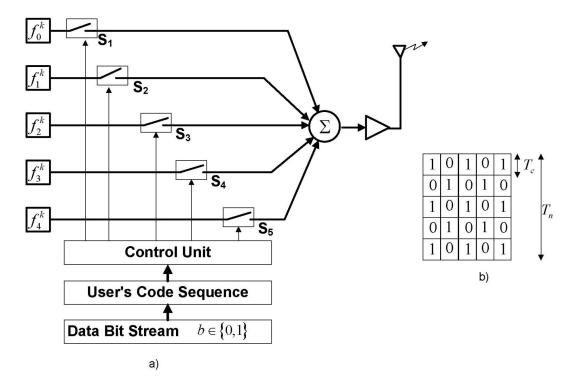

#### 3.3. Superposición de Tonos

La técnica de superposición de tonos establece el proceso de sincronía para establecer comunicación en distintos canales de comunicación simultáneamente [14]. La técnica se implementa en FPGA empleando pipelines estableciendo un sistema computacionalmente eficiente.

En el esquema de superposición de tonos cada chip se transmite en más de una frecuencia simultáneamente. La figura 7 a) muestra el esquema de transmisión por tonos simultáneos. Por cada tiempo de chip se activan 3 ó 2 relays activando la misma cantidad de frecuencias. El salto se continua produciendo cada tiempo de chip, a excepción que en cada tiempo de chip se transmite más de un tono como muestra la figura 7 b).

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

Revista Informática y Sistemas. Vol., No. XX, meses, año, páginas

ISSN 2550-6730

### a) Diagrama del Transmisor.

### b) Diagrama del Receptor.

Figura 6: Esquema de integración SoC-FPGA.

En el esquema de la figura 7 a) el bloque Data Bit Stream representa la fuente de información a transmitir. Este bloque conforma el conjunto de símbolos que se transmitirán por salto como indica el bloque User's Code Sequence. Este bloque implementa el salto rápido por cada bit de información transmitido. El bloque de control acciona los switches para la generación de tonos simultáneos.

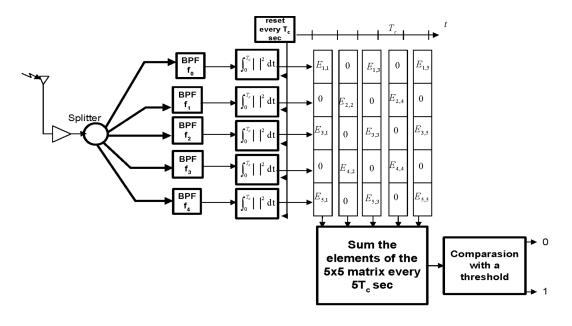

El esquema de recepción se conforma por la colocación en paralelo de filtros pasa-banda como muestra la figura 8 por cada tiempo de chip. En cada banda se conforma un detector de energía para establecer la presencia del tono transmitido en el canal de comunicaciones. La salida de cada rama conforma una matriz empleada para la decodificación de la señal de salto. Con la matriz obtenida a la salida de cada rama se realiza la adición de sus elementos para establecer la transmisión de un cero o un uno.

Aunque los esquemas de transmisión-recepción mostrados en las figuras 7 y 8 solo se describen para la recepción de información por espectro esparcido, su empleo como esquema de sincronismo resulta de igual utilidad. En función de la adición de los elementos de la matriz, a la salida del esquema de la figura 8, se puede establecer un esquema de sincronismo para la generación correcta del código pseudo-aleatorio.

Para la implementación de la recepción, en FPGA se implementa la adición de los elementos de la matriz como muestra el esquema de la figura 8. Los procesos de filtrado pasa-banda y elevación al cuadrado se realizan en su versión analógica.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

A. Arteaga, M. Bring, J. Torres

Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

Figura 7: Esquema del transmisor por superposición de tonos a implementar en FPGA.

#### 3.4. Implementación de modulador FHSS-FSK

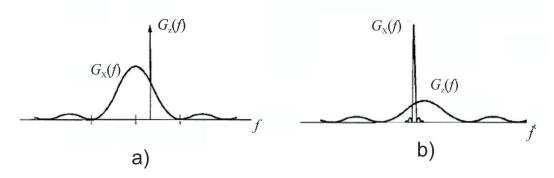

El reporte en [15] muestra la conformación del modulador para el sistema de salto mediante el empleo de sintetizadores digitales de frecuencia (DDFS). El esquema circuital para la implementación del DDFS se conforma en su variante más básica mediante un acumulador de fase y una memoria ROM. Estos bloques se interconectan como muestra la figura 9.

El acumulador de fase conforma la secuencia temporal que evalua la función cosenoidal. Esta secuencia temporal se conforma teniendo en cuenta la frecuencia de entrada. El bloque de memoria ROM almacena la función cosenoidal, la secuencia temporal accede estas posiciones de memoria conformando una secuencia cosenoidal de mayor o menor frecuencia.

Con el objetivo de reducir costes de implementación el sistema DDFS se implementa haciendo uso de la simetría de la secuencia cosenoidal. La figura 10 muestra la conformación del esquema DDFS con el empleo del acumulador de fase y los bloques de memora ROM. Dado que las secuencias cosenoidales tienen simetría impar alrededor de la mitad de su período, esta condición puede emplearse para conformar la secuencia a partir del intervalo entre 0 y  $\frac{\pi}{2}$ . El acumulador de fase conforma la secuencia siempre en el intervalo  $\begin{bmatrix} 0 & \frac{\pi}{2} \end{bmatrix}$  y mediante el empleo de un inversor se conforma la forma de onda coseinodal como muestra la figura 10.

#### 3.5. Tecnologías empleadas y funciones implementadas en el FPGA.

La tabla 1 muestra un resumen de las tecnologías empleadas y sus principales funcionalidades. Como se muestra en la tabla, en la conformación de un sistema de salto en frecuencia en FPGA se emplean dispositivos de Xilinx y Altera. En estos FPGAs se implementan diversas funciones como el sincronismo, la demodulación o el modulador. Entre estos esquemas, la solución más completa por incluir las etapas

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

Revista Informática y Sistemas. Vol. , No. XX, meses, año, páginas

ISSN 2550-6730

Figura 8: Esquema de algoritmo iMPAs para implementar en FPGA.

Figura 9: Esquema para el sintetizador digital de frecuencia DDFS [15].

de detección y sincronismo se reporta por la técnica iMPAs. El resto de los sistemas reportados integra FPGAs con circuitos integrados para lograr el transmisor y el receptor.

### 4. CONCLUSIONES

En la literatura científica se reportan diversas soluciones para la implementación de esquemas FHSS. Entre las soluciones reportadas en FPGA para la transmisión se emplea este dispositivo como generador de la secuencia de salto en forma integrada con un oscilador externo. En menor medida se emplea el FPGA para la conformación de la señal FHSS. En el caso del receptor, el FPGA se integra típicamente con osciladores externos. En menor medida se conforman juntas las etapas de detección y sincronismo en el FPGA.

### 5. RECONOCIMIENTOS

Los autores desean agradecer a la institución CIDP por el apoyo y conducción del proyecto vinculante a esta investigación.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

A. Arteaga, M. Bring, J. Torres Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

Figura 10: Esquema para el sintetizador digital de frecuencia DDFS en FPGA [15].

Tabla 1: Tecnología, Funciones y Parámetros empleados.

| Solución                    | FPGA        |               |

|-----------------------------|-------------|---------------|

|                             | Tecnología  | Funcionalidad |

| iMPAs [11]                  | Stratix 1   | Sincronismo   |

| FPGA-PC [12]                | Spartan3    | DDC           |

| FPGA-SoC [13]               | Altera      | MODEM BFSK    |

|                             |             | Sincronismo   |

| Superposición de Tonos [14] | Spartan IIE | Recepción     |

| Modulador FHSS-FSK [15]     | Statrix 1   | Modulador     |

#### 6. REFERENCIAS

- [1] N. R. Ghate y K. V. Kale. "Smart home safety device using frequency hopping approach based on GSM generation". En: 2017 1st International Conference on Intelligent Systems and Information Management (ICISIM). 2017 1st International Conference on Intelligent Systems and Information Management (ICISIM). Oct. de 2017, págs. 341-347. DOI: 10.1109/ICISIM.2017.8122196.

- J. So e Y. Kim. "Interference-aware frequency hopping for Bluetooth in crowded Wi-Fi networks".

En: Electronics Letters 52.17 (2016), págs. 1503-1505. ISSN: 0013-5194. DOI: 10.1049/el.2016.

- [3] S. Al-Sarawi y col. "Internet of Things (IoT) communication protocols: Review". En: 2017 8th International Conference on Information Technology (ICIT). 2017 8th International Conference on Information Technology (ICIT). Mayo de 2017, págs. 685-690. DOI: 10.1109/ICITECH.2017.8079928.

- [4] Gang Wang y col. "Spread spectrum design for aeronautical communication system with radio frequency interference". En: 2015 IEEE/AIAA 34th Digital Avionics Systems Conference (DASC). 2015 IEEE/AIAA 34th Digital Avionics Systems Conference (DASC). Sep. de 2015, págs. 1-26. DOI: 10.1109/DASC.2015.7311549.

- [5] V. Kafedziski y S. Pecov. "Implementation of a high resolution stepped frequency radar on a USRP". En: 2017 13th International Conference on Advanced Technologies, Systems and Services in Telecommunications (SIKS). 2017 13th International Conference on Advanced Technologies, Systems and Services in Telecommunications SIKS). Oct. de 2017, págs. 236-239. DOI: 10.1109/SKS.2017.8246271.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

Revista Informática y Sistemas. Vol., No. XX, meses, año, páginas

ISSN 2550-6730

- [6] Multi-Carrier Spread Spectrum & Related Topics. Softcover reprint of the original 1st ed. 2000 edition. Boston, MA, 2012. ISBN: 978-1-4613-7010-9.

- [7] G. F. Elmasry. "The progress of tactical radios from legacy systems to cognitive radios". En: *IEEE Communications Magazine* 51.10 (oct. de 2013), págs. 50-56. ISSN: 0163-6804. DOI: 10.1109/MCOM. 2013.6619565.

- [8] R. A. Scholtz. "The Origins of Spread-Spectrum Communications". En: *IEEE Transaction on Communications* COM-30.5 (1982).

- [9] N. Wiener. Extrapolation, Interpolation and Smoothing of Stationary Time Series. New York: John Wiley & Sons, 1950.

- [10] C.E. Shannon. "A Mathematical Theory of Communication". En: Bell System Tech. J. 27 (1948), págs. 379-423.

- [11] W. Wang y Z. Wang. "FPGA implementation of rapid PN code acquisition using iterative message passing algorithms". En: *IEEE Aerospace and Electronic Systems Magazine* 29.6 (jun. de 2014), págs. 13-23. ISSN: 0885-8985. DOI: 10.1109/MAES.2014.120228.

- [12] M. Rakhshanfar, M. Teimouri y Z. HassanShahi. "Implementation of Software Radio Based on PC and FPGA". En: 2008 4th IEEE International Conference on Circuits and Systems for Communications. 2008 4th IEEE International Conference on Circuits and Systems for Communications. Mayo de 2008, págs. 633-637. DOI: 10.1109/ICCSC.2008.140.

- [13] H. Lu y B. Lian. "The Design and Implementation of Spread Spectrum Base-Band System Based on Software Radio". En: 2008 4th International Conference on Wireless Communications, Networking and Mobile Computing. 2008 4th International Conference on Wireless Communications, Networking and Mobile Computing. Oct. de 2008, págs. 1-4. DOI: 10.1109/WiCom.2008.331.

- [14] E. Inaty y R. Ayoubi. "FPGA-based transmitter-receiver architecture of an overlapped FFH-CDMA system: design and simulation". En: 2006 IEEE International Symposium on Circuits and Systems. 2006 IEEE International Symposium on Circuits and Systems. Mayo de 2006, 4 pp.-2800. DOI: 10.1109/ISCAS.2006.1693205.

- [15] G. Bouzid y col. "FPGA implementation of FHSS-FSK modulator". En: 2008 3rd International Conference on Design and Technology of Integrated Systems in Nanoscale Era. 2008 3rd International Conference on Design and Technology of Integrated Systems in Nanoscale Era. Mar. de 2008, págs. 1-5. DOI: 10.1109/DTIS.2008.4540261.

- [16] Bernard Sklar. Digital Communications, Fundamentals and Applications. Second. New Jersey: Prentice Hall, 2001. 953 pagetotals. ISBN: 0130847887.

- [17] A. B. Carlson, P. B. Crilly y J. C. Rutledge. Communication Systems: An introduction to Signals and Noise in Electrical Communication. Fourth Edition. New York, NY, USA: McGraw-Hill, 2002. 853 pagetotals. ISBN: 0-07-011127-8.

- [18] M. K. Simon y col. Spread Spectrum Communications Handbook. McGraw-Hill Inc., 2002.

- [19] J. S. Min y H. Samueli. "Analysis and design of a frequency-hopped spread-spectrum transceiver for wireless personal communications". En: *IEEE Transactions on Vehicular Technology* 49.5 (sep. de 2000), págs. 1719-1731. ISSN: 0018-9545. DOI: 10.1109/25.892577.

#### SOBRE LOS AUTORES

Alejandro Arteaga Pérez, Ingeniero en Telecomunicaciones y Electrónica, se encuentra realizando la maestría en Sistemas de Telecomunicaciones, desarrollador de aplicaciones para las comunicaciones en CIDP-Grito de Baire.

Miguel Angel Bring Fernández, Ingeniero en Telecomunicaciones y Electrónica, desarrollador de aplicaciones para las comunicaciones en CIDP-Grito de Baire.

### REVISTA DE TECNOLOGÍAS DE LA INFORMÁTICA Y LAS TELECOMUNICACIONES

A. Arteaga, M. Bring, J. Torres

Sistemas de Espectro Esparcido por Salto de Frecuencia en FPGA

Jorge Torres Gómez, Ingeniero en Telecomunicaciones y Electrónica, Master en Sistemas de Telecomunicaciones, Doctor en Ciencias Técnicas, se encuentra trabajando como profesor Auxiliar en la Facultad de Telecomunicaciones y Electrónica, CUJAE.